发布日期:2026/04/20

盛邦安全200Gbps高速链路加密网关的发布,引发产学研用各界广泛关注。其超高速、低延迟的极致性能背后的技术逻辑是什么?基于开放合作的理念,我们特邀产线技术专家对核心技术架构与实现路径进行深度解析。

直面困境:三条路线的艰难选择

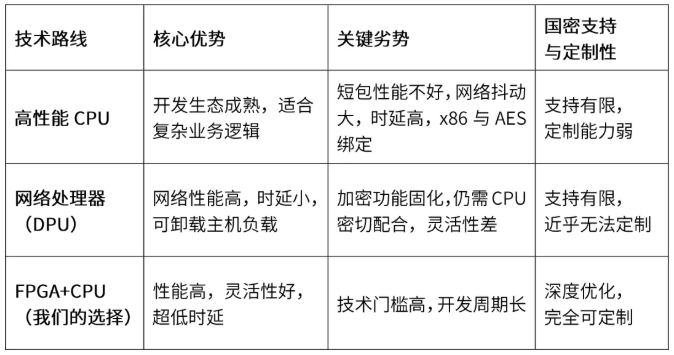

在高速网络加密的技术实现路径中,业界主要形成了三种主流方案:基于高性能CPU的通用架构、基于网络处理器(Data Processing Unit, DPU)的专用架构,以及基于现场可编程门阵列(Field Programmable Gate Array, FPGA)+CPU的异构架构。通过对三种方案的深入分析与对比,我们最终选择FPGA+CPU异构架构作为200Gbps线速加密的核心技术路线。

(1)基于高性能CPU的通用架构

该方案以高性能通用处理器(如Intel X86架构CPU)为核心,结合数据平面开发工具包(Data Plane Development Kit, DPDK)软件加速技术与专用加密加速卡(如英特尔QuickAssist Technology, QAT)。其优势在于软件开发生态成熟,实现难度较低,可快速响应复杂上层业务逻辑变化。然而,其局限性同样显著:其一,该方案高度依赖X86架构,加密算法以高级加密标准(Advanced Encryption Standard, AES)等国际通用算法为主,对国密算法(如SM2、SM3、SM4)的原生支持能力与性能优化水平不足;其二,在处理海量小数据包(如64字节)时,CPU中断与系统调度的overhead会成为显著瓶颈,导致网络延迟增加及性能抖动,高负载场景下难以保障业务性能的稳定性。

(2)基于DPU的专用架构

DPU是近年来针对数据中心场景推出的专用处理器,其设计目标是将网络转发、存储管理等基础功能从主机CPU卸载,以提升数据中心的整体资源利用率与处理效率。以NVIDIA BlueField系列为代表的DPU,在网络协议处理与数据转发方面表现出色,可显著降低主机CPU负载。然而,DPU的技术焦点仍集中在网络协议卸载,其内置固定功能加密引擎通常仅支持AES等基础算法,难以满足高性能国密算法的定制化需求;同时,复杂网络包处理与数据面控制仍需CPU密切配合,未实现加密业务的完全卸载,在极致加密性能场景下灵活性不足且成本效益不高。

(3)基于FPGA+CPU的异构架构

该方案采用FPGA作为高性能数据处理平面,承担实时高速网络协议解析与数据加解密任务;CPU作为控制平面,专注于系统管理、策略配置等上层逻辑处理。这种架构具备以下不可替代的优势:其一,极致性能:通过硬件并行流水线设计,FPGA可实现固定超低延迟的网络数据处理,满足200Gbps线速要求且性能无抖动;其二,自主可控:可针对国密算法进行底层电路级至架构级的深度定制与优化,性能远超通用处理器;其三,数据平面完全卸载:从链路层(MAC)至加密层(ESP)的全流程处理均在FPGA内完成,彻底解放主机CPU。当然,该方案的技术门槛极高,需融合硬件设计、高速网络与密码学等多领域关键技术。

通过对性能、灵活性、国密合规要求及长期技术自主性的综合评估,FPGA+CPU异构架构成为200Gbps线速加密的最优选择。该架构同时满足200Gbps线速、超低延迟、国密算法支持与自主可控的严苛要求,是产品的核心基石与技术自信来源。

克艰之路:从10Gbps到200Gbps的关键技术突破

从10Gbps网络密码机到200Gbps线速加密网关的产品升级,并非简单的性能数值提升,而是涉及架构设计、算法实现与工程优化的全面技术跨越。我们主要突破了以下四大核心技术难关:

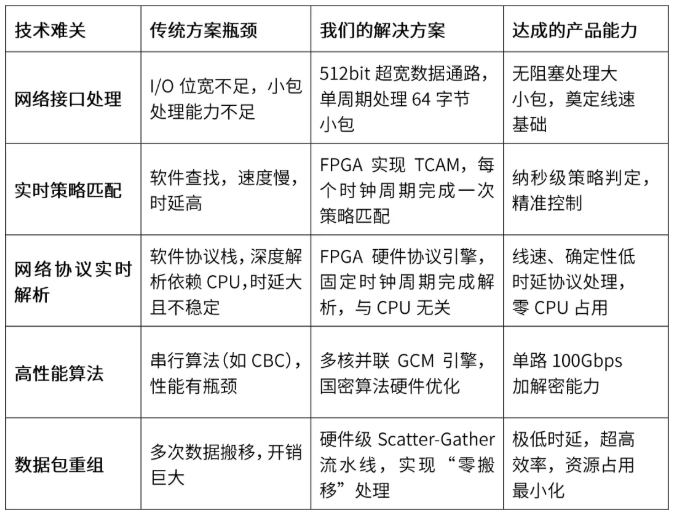

(1)网络接口处理:海量数据的“零阻塞”吞吐设计

单个网络接口100Gbps带宽意味着设备需每秒处理约1.4亿个数据包(按最小64字节包计算),传统架构的I/O瓶颈难以突破。我们充分利用FPGA的并行与流水线特性,将内部数据处理位宽扩展至512bit,实现每时钟周期“吞入”或“吐出”一个完整的64字节小数据包。这种设计使数据流在FPGA内部形成“无阻塞通道”,从源头上消除了I/O瓶颈,为200Gbps线速处理奠定了基础。

(2)实时策略匹配:纳秒级流量识别的硬件实现

面对每秒上亿的数据包,需在纳秒级时间内完成“感兴趣流”的识别与策略匹配(加密或明文转发),传统软件算法无法满足需求。我们创新性地采用并行压缩比特向量(Compressed Bit Vector, CBV)算法,通过硬件逻辑模拟三态内容寻址存储器(Tri-State Content Addressable Memory, TCAM)的高效查找功能,并设计了5级流水线架构,实现每个时钟周期完成一次五元组(源IP、目的IP、源端口、目的端口、协议类型)策略匹配,精准判定数据包处理策略。

(3)网络协议解析:多层协议的实时识别与重构

数据包结构复杂,涵盖链路层(MAC、VLAN)、网络层(IPv4、IPv6)及加密专用层(ESP)等多层协议,需在高速流转中完成实时解析与处理。我们在FPGA内部构建了链路层与网络层协议处理引擎,实现了多层协议的无缝解析与重构,为后续加密与封装步骤提供了精准的结构化数据输入。

(4)数据重组与整形:硬件级“零搬移”处理流水线

加密认证会改变数据包长度与结构,传统“拆包-处理-重组”模式会带来巨大数据搬移开销。我们借鉴软件领域的分散-聚集(Scatter-Gather)技术理念,在FPGA内部设计了硬件级处理流水线:数据包进入流水线后,通过描述符(Descriptor)预先规划MAC头、IP头、载荷、封装安全载荷(Encapsulating Security Payload, ESP)尾等字段的存储位置;加密、认证等模块并行完成处理后,流水线末端根据描述符指引,将分散存储的数据段按顺序高效聚集,重组为完整数据包。这种设计的核心优势在于“数据零搬移”——数据仅沿流水线流动,无需为处理而来回迁移,极大提升了加密整形效率,简化了模块功能设计。

上述技术突破不仅实现了2路100Gbps接口的200Gbps线速加解密能力,更构建了深厚的技术壁垒。

硬核成果:权威认证加持,彰显自主可控实力

经中国信息通信研究院(CAICT)泰尔实验室的权威检测验证,该产品实现了2路100Gbps接口的线速加解密能力,总计吞吐量达200Gbps,多项核心技术指标取得突破性进展。

(1)极速吞吐

权威测试数据显示,产品双通道加密吞吐量达195Gbps以上,接近200Gbps的理论极限,为海量数据传输提供了“零降速”的安全保障。

(2)超低延迟

产品最大处理延迟小于3微秒,在超高速通信场景中,微秒级延迟优化对业务实时性至关重要,该指标显著提升了业务系统的实时响应能力。

(3)合规可控

深度优化SM2/SM3/SM4国密算法,技术体系完全自主可控,通过商用密码产品认证,满足高安全等级的数据传输需求。

历经数百个日夜的研发与打磨,盛邦安全200Gbps高速链路加密网关终于正式亮相,一经发布便引发产学研用各界广泛关注,核心指标表现亮眼,用实力彰显中国网络安全企业的自主创新能力。

初心不改:技术迭代不止,开放合作共赢

在数字化转型加速的背景下,网络流量呈指数级增长,传统安全设备已无法满足新时代的高性能需求,200Gbps线速网络密码机应运而生。通过FPGA+CPU异构架构的优化与关键技术突破,我们不仅实现了性能的极致追求,更打造了一款适配中国场景、满足中国需求的高性能安全产品。

从技术选型的艰难抉择,到攻克难关的咬牙坚持;从实验室里的反复调试,到权威认证的亮眼成果;盛邦安全用实际行动证明,中国网络安全企业,有能力、有实力突破核心技术壁垒,用自主创新守护数字世界的安全与有序。未来,盛邦安全将持续深耕高速加密领域,一方面持续优化算法实现,探索更高性能的加密架构;另一方面加强对新兴网络协议与标准的适配,不断完善产品矩阵,满足更多行业场景的安全需求。

目前,盛邦安全200Gbps高速链路加密网关已正式面向市场,诚邀各领域合作伙伴垂询对接,共同探索高速链路加密技术在卫星互联网、智算中心、金融、政务等场景的深度应用,构建安全高效的网络生态,共筑国家网络空间安全屏障!